GateForge Consulting Ltd.

Custom FPGA logic design and software development services.

I primarily offer custom FPGA logic design services and related software

development. I follow a System Design

Standard refined over many projects.

I have over 15 years of experience with Quartus, Vivado, and ISE for

consumer and industrial applications on Zynq devices, scientific

instrumentation on Kintex-7, space-rating validation on Spartan-6Q, ASIC

emulation on Virtex-7, image processing and system infrastructure on Artix-7,

and real-time video processing on Virtex UltraScale+ on Amazon's F1 cloud

service.

I mainly work in Verilog-2001, and take great effort in writing modular,

portable, and cleanly synthesizable code, following my in-house Verilog Coding Standard and using my library of FPGA Design Elements. I can also

deliver work in VHDL and other HDLs as required by my clients.

I have 30 years of experience working in Linux environments, spanning

everything from system administration to kernel programming. In software, I

have worked in about a dozen programming languages, but primarily in C, Python,

and assembly (MIPS, ARM, 6502), and occasionally in Perl and Forth.

Contact

- gateforge@fpgacpu.ca

- Twitter

- LinkedIn

- vCard

- QR Code

Client Projects

- Design and implementation of a floating-point complex-number linear

algebra accelerator (covariance matrix generation, eigenvector estimation, and

eigenvalue calculation) for real-time sensor data processing in a medical

device, including simulation and verification against original software

calculations.

- Complete redesign of a research satellite's 10 Gb/s optical sensor

interface from a Spartan-6 to an Artix-7 device, including a non-standard

SERDES interface, data repacking, DDR3 memory interfacing, and SPI interface to

host computer. Launched in summer 2024.

- Design of a multi-axis feedback position control and data processing

system for industrial R&D, with a custom Network-on-Chip, high-precision

(100+ bit) integer processing pipeline, and host-side Python control software,

running on an AMD/Xilinx Zynq 7020.

- Updated a legacy silicon fabrication industrial control EtherCAT

interface from a proprietary Spartan-6/TigerSHARC system to a dual-core Zynq

device, with extensions to work in a real-time dual-OS environment (PetaLinux

and FreeRTOS).

- Redesign of high-speed ADC SERDES interfaces for a port from Spartan-6

to Kintex-7 devices, improved with data frame self-alignment.

- Rebuild of SEU (Single Event Upset) test circuits from Virtex-5 to

Virtex-7, with new interfaces to legacy TID (Total Ionizing Dose) testing

hardware. These circuits are used to test FPGAs under proton and heavy ion

beam exposure.

- Implementation of space-rating test cases for defense-grade Spartan-6Q

devices. These tests reach the extremes of I/O standards, SERDES and PLL

operating ranges, pin leakage currents, and delays.

- Design and implementation of custom interfaces to multiple CPUs, DDR2

RAM, a camera, and custom AXI peripherals in a medical device. Board design

reviews to update system from Spartan-6 to Artix-7.

- Debugging Closed Caption extraction from XDCAM video for a broadcasting platform.

- Integration of real-time video processing IP, ML acceleration for

object detection, multiple DDR4 controllers, and multiple video encoding IPs on

an AMD/Xilinx Virtex Ultrascale+ board, with custom-built AXI address

re-mapping logic to relocate IP in the address space. Wrote the multi-core

host software to communicate with the FPGA and process multiple raw 1080p30

video streams in parallel.

- Conversion of a set-top box video compositing product onto Amazon's F1

cloud FPGA platform, including FPGA floorplanning, build debug, and timing

closure, and creation of core application software and related AWS

infrastructure.

- Set-top audio and video format conversion on an AMD/Xilinx Zynq device

and interfacing to H.264 encoding hardware. Shipped to over 1000 customers.

Internal Projects

- FPGA Design Elements

A reference library of fundamental (and advanced) digital logic design elements, along with standards for Verilog coding and system design. Think of it as a hardware analog to the C Standard Library ("libc") and its documentation.

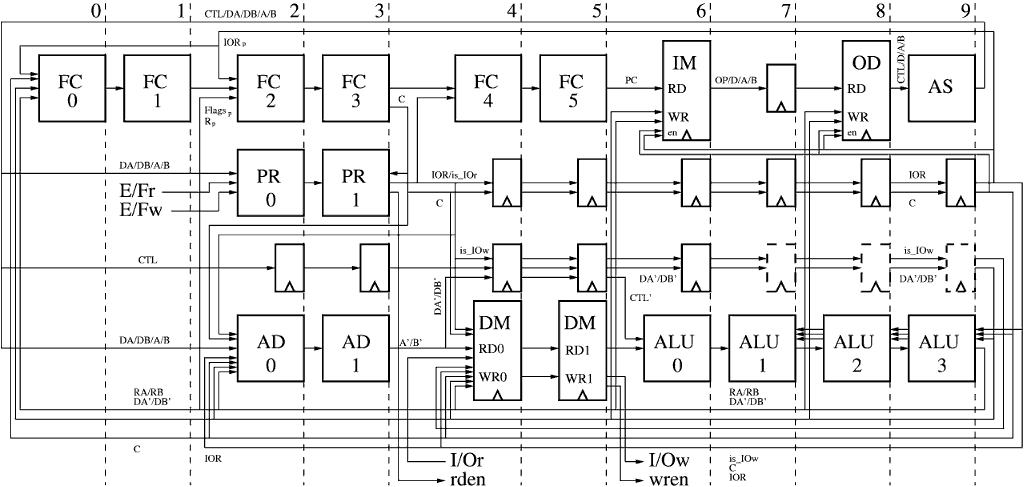

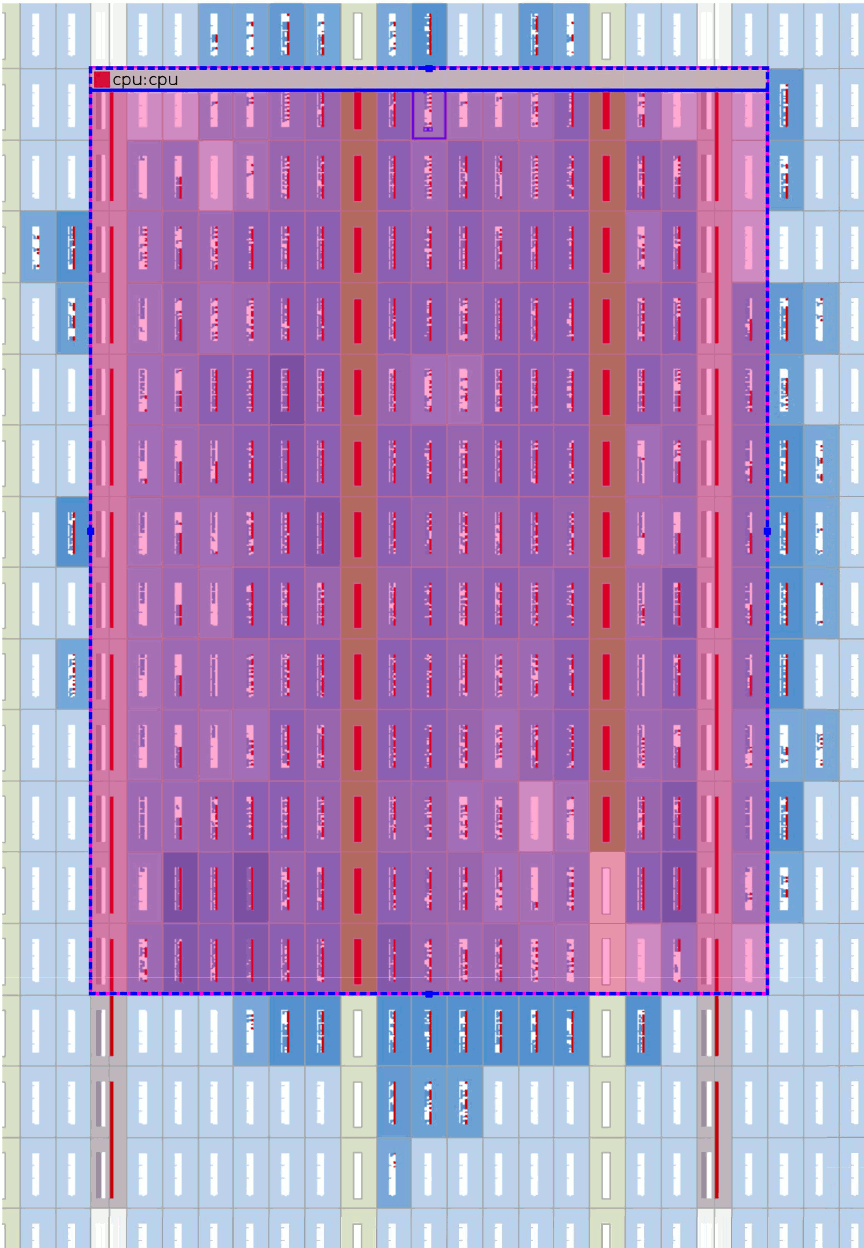

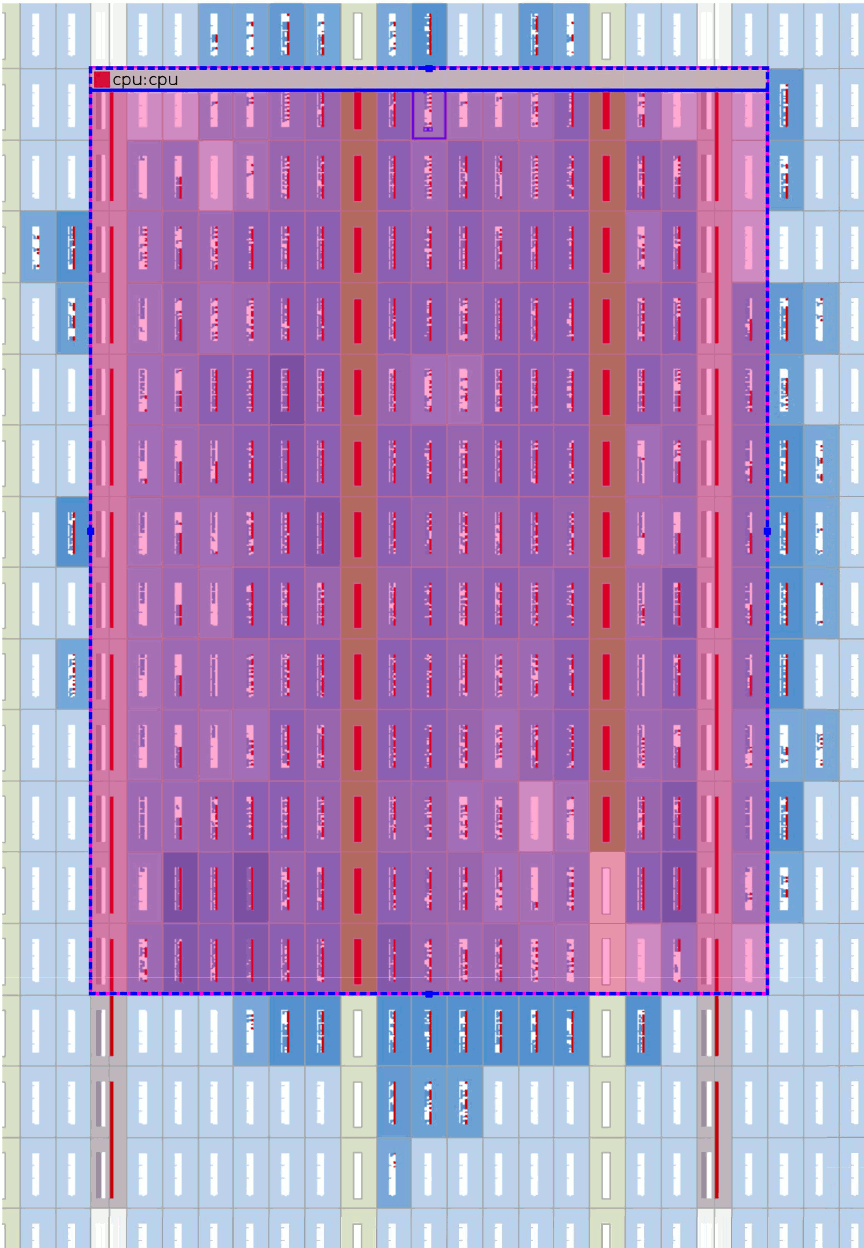

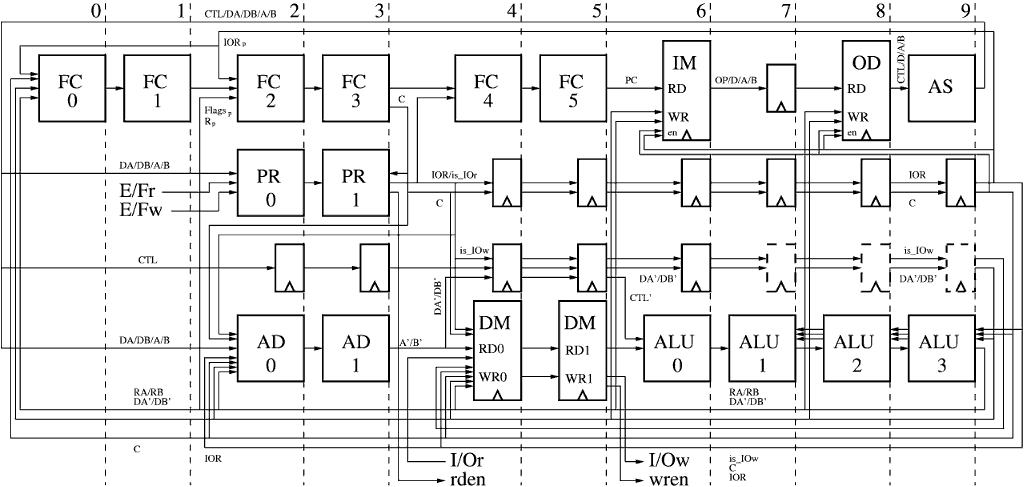

- The Octavo Soft-Processor

Technology demonstrator. Open-Source soft-processor for high-performance, aimed at rapid FPGA system development.

GitHub repository

Publications

Some examples of past FPGA design research. You can find a complete list at the Publications page.

- Octavo: An FPGA-Centric Processor Family

Charles Eric LaForest and J. Gregory Steffan

ACM International Symposium on Field-Programmable Gate Arrays (FPGA), February 2012, Monterey

Using our own design techniques, we show it is possible to create very high-speed (500+MHz) soft-CPUs on FPGAs, along with fast I/O, memory, and multipliers.

- Composing Multi-Ported Memories on FPGAs

Charles Eric LaForest, Zimo Li, Tristan O'Rourke, Ming G. Liu, J. Gregory Steffan

ACM Transactions on Reconfigurable Technology and Systems (TRETS), August 2014, Volume 7, Issue 3, Article No. 16

We present a thorough exploration and evaluation of the design space of FPGA-based soft multi-ported memories for conventional solutions, and also for the recently-proposed Live Value Table (LVT) and XOR approaches to unidirectional-port memories, reporting results for both Altera and Xilinx FPGAs.

fpgacpu.ca